芯片封裝工藝

引言

提起芯片,大家應該都不陌生。芯片,作為集成電路(Integrated Circuit,IC)的載體,是一項世界各國都在大力發展研究的高科技產業。IC產業主要由IC設計業、IC制造業及IC封測業三個部分組成。在本文中,我們將帶大家認識一下IC封測業中的芯片封裝技術。

02何謂芯片封裝

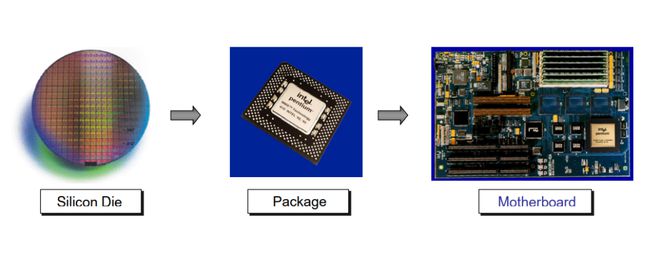

圖 1 芯片封裝的定位(圖片來源老師課件)

生活中說起封裝,可能就是把東西放進箱子,然后用膠帶封口,箱子起到的最大作用也就是儲存,將箱子里面與箱子外面分隔開來。但在芯片封裝中,“箱子”可有著更大的作用。安裝集成電路芯片用的外殼,它不僅起著安放、固定、密封、保護芯片和增強導熱性能的作用,而且還是溝通芯片內部世界與外部電路的橋梁——芯片上的接點用導線連接到封裝外殼的引腳上,這些引腳又通過印刷電路板上的導線與其他器件建立連接。

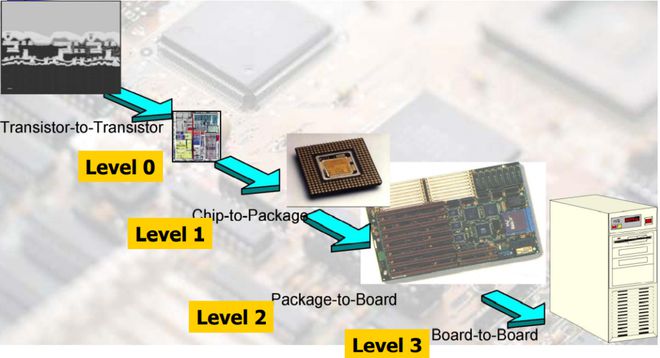

從由硅晶圓制作出來的各級芯片開始,芯片的封裝可以分為三個層次,即用封裝外殼將芯片封裝成單芯片組件(Single Chip Module,簡稱SCM)和多芯片組件(MCM)的一級封裝,也稱為片級封裝;將一級封裝和其他元器件一同組裝到印刷電路板(PWB)(或其它基板)上的二級封裝,也稱為板級封裝;以及再將二級封裝插裝到母板上的三級封裝,也稱為系統級封裝。

圖 2 芯片封裝分級(圖片來源老師課件)

其實,在一、二、三級封裝與IC芯片之間還有一個步驟,被稱為芯片互連級封裝,其主要作用就是通過互連技術將IC芯片焊區與各級封裝的焊區連接起來,也就是讓芯片能夠通過外殼與外界產生交流,零級封裝也被稱為芯片互連級。

03芯片封裝的功能

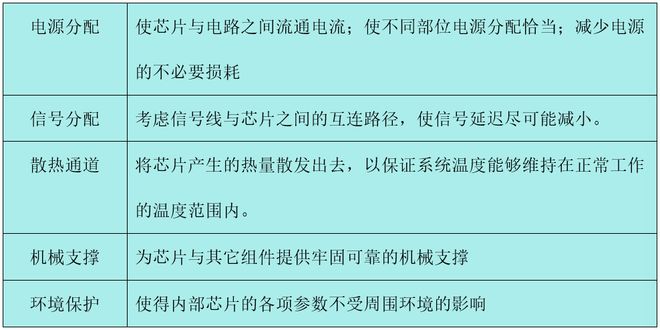

表 1 芯片封裝的五大功能

04芯片封裝的幾種技術

4.1 芯片互連技術

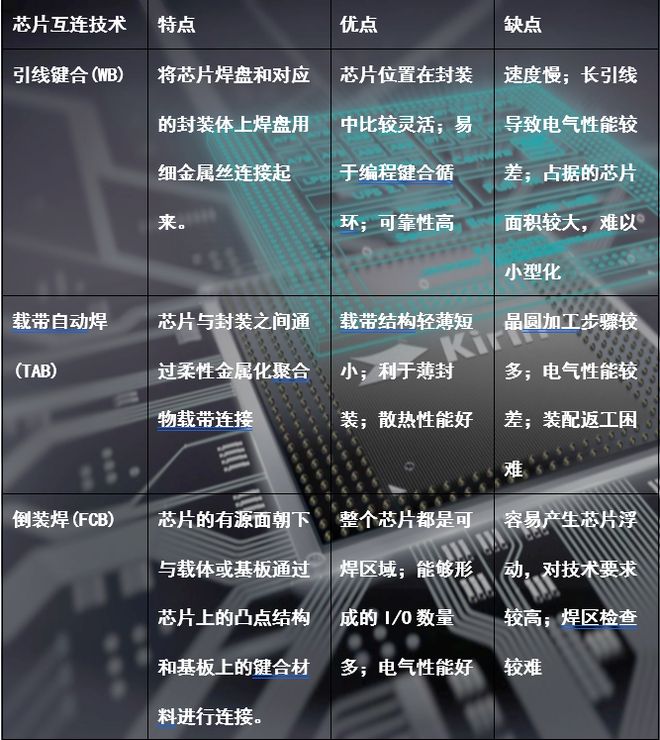

芯片互連技術來自與我們上文提到的零級封裝,這是芯片與封裝外殼以及外界環境建立聯系的關鍵技術。芯片互連技術主要有三種:引線鍵合、載帶自動焊以及倒裝焊。

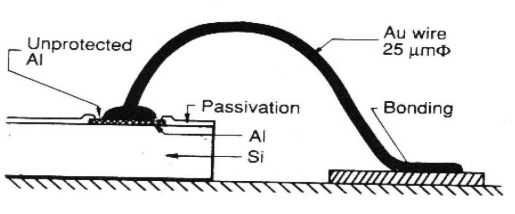

(a) 引線鍵合

圖 3 引線鍵合示意圖

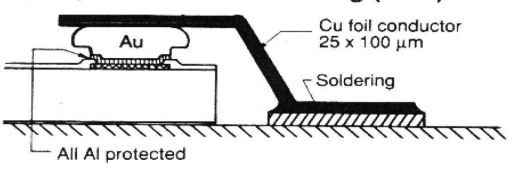

(b) 載帶自動焊

圖 4 載帶自動焊示意圖

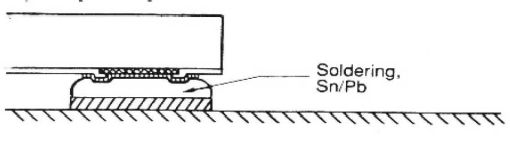

(c) 倒裝焊

圖 5 倒裝焊示意圖

表 2 三種芯片互連技術對比

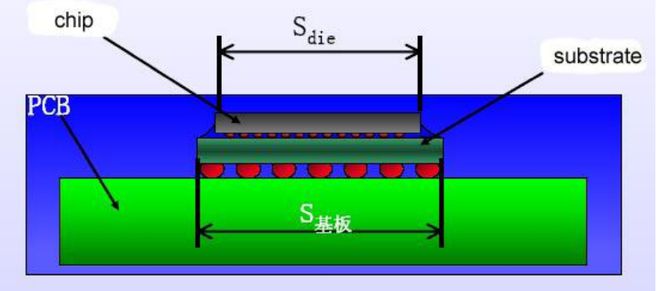

4.2 BGA封裝技術

圖 6 BGA封裝

BGA(Ball Grid Array):球柵陣列。它是在基板的下邊按面陣方式引出球形引腳,在基板上面貼裝大規模集成電路芯片,是大規模集成電路芯片常用的一種表面貼裝型封裝形式。

優點:BGA封裝的封裝尺可以做的更小,同時也更節省PCB板的布線面積。

缺點:電路板的彎曲應力導致潛在的可靠性問題,BGA封裝更容易受到壓力

4.3 CSP封裝技術

CSP(Chip Size Package),即芯片尺寸封裝。是指封裝尺寸不超過裸芯片1.2倍的一種先進的封裝形式(美國JEDEC標準)。CSP技術是在對現有的芯片封裝技術,其是對成熟的BGA封裝技術做進一步技術提升的過程中,不斷將各種封裝尺寸進一步小型化而產生的一種封裝技術。

優點:體積小;可容納引腳數多;電性能良好;散熱性能好

圖 7 CSP結構示意圖(圖片來源網絡)

05未來封裝技術的展望

現在,IC產業中芯片的封裝與測試已經與IC設計和IC制造一起成為了密不可分又相對獨立的三大產業,往往設計制造出的同一塊芯片卻要采用各種不同的封裝形式與結構,在未來芯片封裝又將如何發展呢?在這一部分將為大家介紹未來封裝產業的發展趨勢以及幾種先進的可能占據未來市場的封裝技術。

5.1 未來封裝技術的幾大趨勢

(1) 由有封裝向少封裝和無封裝發展

(2) 無源器件走向集成化

(3) 3D封裝技術

5.2 晶圓級封裝(WLP)技術

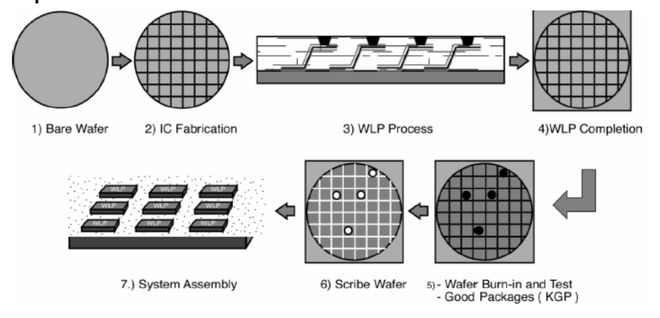

圖 8 WLP技術流程(圖片來源老師課件)

WLP是Wafer Level Packaging的縮寫。晶圓級封裝, 就是在硅片上依照類似半導體前段的工藝, 通過薄膜、光刻、電鍍、干濕法蝕刻等工藝來完成封裝和測試, 最后進行切割, 制造出單個封裝成品。

優勢:封裝工藝簡化以及封裝尺寸小。

5.3 SOC & SIP

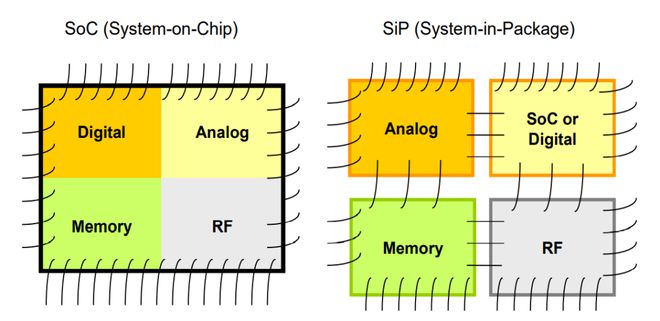

SOC(System on Chip),即片上系統,指的是將實現系統功能的各個模塊集成到一個芯片上。這意味著在單個芯片上,就能完成一個電子系統的功能。

圖 9 SOC與SIP對比示意圖(圖片來源網絡)

SIP是System in a Packaging的縮寫,指的是將幾個實現不同模塊功能的芯片放到一個封裝中去。

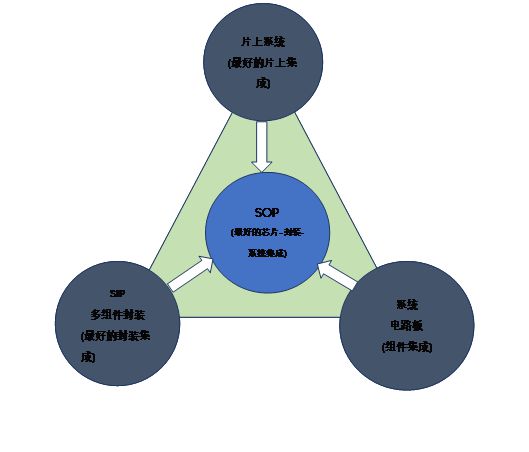

5.4 SOP

圖 10 SOP的地位(圖片自制)

SoP是System-on-package的縮寫,是被提出來作為整合系統的概念,希望將數字、模擬、射頻、微機電、光學電路或次系統都整合在封裝上,除了提高系統整合程度外,同時亦保有可接受的成本效益。SOP的另一個優點是與SOC及SIP兼容,SOC與SIP均可視為SOP的次系統,一起被整合在封裝上。